#### **BMR511**

# 2-phase integrated power stage up to 140 A peak

The BMR511 is a two-phase integrated power stage with a continuous output current of 80A, and a peak current of 140 A.

It comes in a compact footprint of just  $0.9 \text{ cm}^2 / 0.14 \text{ in}^2$  and is available with either LGA or solder bump termination.

The device is designed with the power stages located on bottom for the most effective down stream conducted cooling, and delivers excellent thermal results.

The BMR511 features protection mechanisms such as over-current protection and over-temperature protection. Two enable inputs are provided for each phase, and the module accepts tri-state PWM inputs.

### **Key features**

- High efficiency:

- 1.8V up to 94.5% at light load, 92.5% at full load.

- 0.75V up to 92% at light load, 88% at full load.

- Can be paralleled with other units

- Remote control

- Reporting temperature and current for each phase

- Excellent thermal performance

- Halogen-free

### Soldering methods

Reflow soldering, LGA and solder bump options

### Key electrical information

| Parameter            | Values               |

|----------------------|----------------------|

| Input voltage range  | 5 - 15 V             |

| Output voltage range | 0.5 - 1.8 V          |

| Max output current   | 80 A TDC/ 140 A peak |

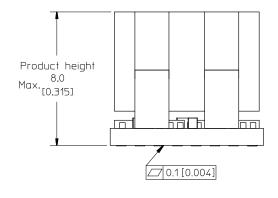

#### Mechanical

10 x 9 x 8 mm / 0.39 x 0.35 x 0.31 in

## **Application areas**

- Designed for AI applications

- Used by CPU, GPUs, IPUs, high-performance ASICSs

# **Product options**

The table below describes the different product options.

|                          | BMR511 | 1 | 04 | 4 | /002 | С | Definitions                              |

|--------------------------|--------|---|----|---|------|---|------------------------------------------|

| Product family           | BMR511 |   |    |   |      |   |                                          |

| Mounting options         |        | 1 |    |   |      |   | 0 = solder bump<br>1 = LGA               |

| Product variants         |        |   | 04 |   |      |   | 04 = standard electrical variant         |

| Mechanical configuration |        |   |    | 4 |      |   | 4 = standard mechanical configuration    |

| Configuration code       |        |   |    |   | /002 |   | /002 = 2 phases                          |

| Packaging options        |        |   |    |   |      | С | C = Antistaic tape and reel<br>packaging |

For more information, please refer to <u>Part 2 Mechanical information</u>.

If you do not find the variant you are looking for, please contact us at <u>Flex Power Modules</u>.

# Order number examples

| Part number     | Vin    | outputs   | configuration                                    |

|-----------------|--------|-----------|--------------------------------------------------|

| BMR5111034/001C | 5-15 V | 0.5-1.8 V | Standard 2 phase module, tape and reel packaging |

### **Absolute maximum ratings**

Stress in excess of our defined absolute maximum ratings may cause permanent damage to the converter. Absolute maximum ratings, also referred to as non-destructive limits, are normally tested with one parameter at a time exceeding the limits in the electrical specification.

| Characteristics                  |                    | min  | typ | max     | Unit |

|----------------------------------|--------------------|------|-----|---------|------|

| Operating temperature (TP1)      |                    | -40  |     | 125     | °C   |

| Storage temperature              |                    | -40  |     | 125     | °C   |

| Input voltage (V <sub>in</sub> ) |                    | -0.3 |     | 20      | V    |

| Signal I/O voltage               | EN, PWM,ISEN, TSEN | -0.3 |     | VCC+0.3 | V    |

| Driver and logic supply          | VCC                | -0.3 | 3.3 | 4       | V    |

### Reliability

Failure rate ( $\lambda$ ) and mean time (50%) between failures (MTBF= 1/ $\lambda$ ) are calculated based on *Telcordia SR*-332 Issue 4: Method 1, Case 3, (80% of  $I_{out}$ ,  $T_{P1}$ =40°C).

|                                         | Mean  | 90% confidence level | Unit        |

|-----------------------------------------|-------|----------------------|-------------|

| Steady-state failure rate ( $\lambda$ ) | 14    | 21                   | nfailures/h |

| Standard deviation ( $\sigma$ )         | 5.5   |                      | nfailures/h |

| MTBF                                    | 70.13 | 46.97                | MHr         |

1/28701-BMR 511 Rev B 2023-06-16 3

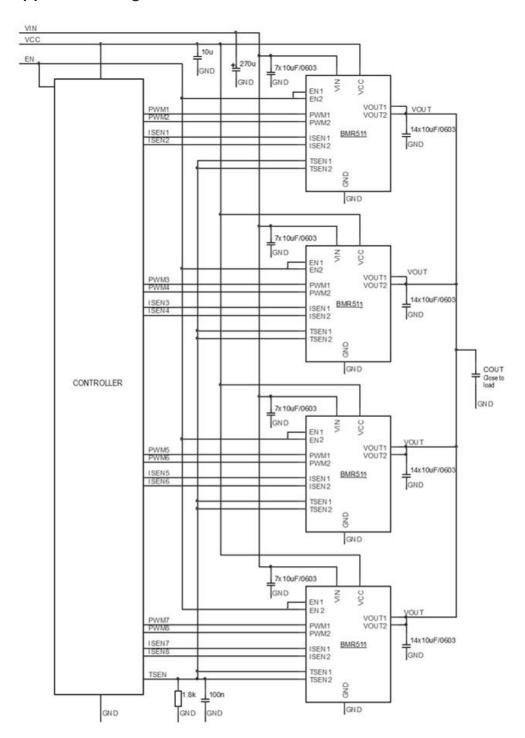

# Typical application diagram

### Typical application circuit for 8 phase rail

#### Notes:

- 1. Value of output capacitance will depend on the application and load transient requirements.

- 2. TSEN filter values might be adjusted if connecting together TSEN of more than 16 phases.

# Electrical specifications for BMR511 — Control and Monitoring

$T_{P1}$  = -40 °C to 125 °C, VI = 12 V, VCC = VEN = 3.3 V, unless otherwise specified under Conditions.

Typical values given at:  $T_{P1}$  = +25 °C, unless otherwise specified under Conditions.

| Characte                                     | eristics                                          | Conditions                                                               | min | typ  | max  | Unit  |

|----------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------|-----|------|------|-------|

|                                              |                                                   | Rising threshold                                                         |     | 2.5  | 3.0  | V     |

| UVLO <sub>VIN</sub> VIN Under Voltage Lock-C |                                                   | Hysteresis                                                               |     | 200  |      | mV    |

|                                              | VCC Under Voltage Lock-                           | Rising threshold                                                         |     | 2.75 | 2.95 | V     |

| UVLO <sub>VCC</sub>                          | Out                                               | Hysteresis                                                               |     | 200  |      | mV    |

| VIL_EN                                       | EN input low threshold                            |                                                                          |     |      | 0.9  | V     |

| V <sub>IH_EN</sub>                           | EN input high threshold                           |                                                                          | 1.4 |      |      | V     |

| V <sub>IL_PWM</sub>                          | PWM input low threshold                           |                                                                          |     |      | 0.6  | V     |

| V <sub>IH_PWM</sub>                          | PWM input high threshold                          |                                                                          | 2.6 |      |      | V     |

| V <sub>TRI_PWM</sub>                         | PWM tri-state region                              |                                                                          | 1.1 |      | 2.1  | V     |

| VHIZ_PWM                                     | PWM high impedance voltage                        |                                                                          |     | 1.6  |      | V     |

|                                              | D)4/4 4 3 1 /                                     | PWM = 0 V                                                                |     | 500  |      | μA    |

| I <sub>PWM</sub>                             | PWM sink/source current                           | PWM = 3.3 V                                                              |     | -500 |      | μA    |

| t <sub>PWM</sub>                             | PWM minimum pulse width                           |                                                                          |     | 15   |      | ns    |

| V <sub>O_TSEN</sub>                          | TSEN voltage when fault                           |                                                                          | 3.0 | 3.3  |      | V     |

| G <sub>TSEN</sub>                            | TSEN gain                                         |                                                                          |     | 8    |      | mV/°C |

| Otsen                                        | TSEN offset                                       | T <sub>J</sub> = +25 °C                                                  |     | 800  |      | mV    |

| T <sub>TSEN</sub>                            | TSEN overtemperature shut-<br>down and fault flag |                                                                          |     | 160  |      | °C    |

| <u> </u>                                     | ISEN agin                                         |                                                                          |     | 5    |      | μA/A  |

| GISEN                                        | ISEN gain                                         | Accuracy                                                                 | -2  | 0    | 2    | %     |

| Oisen                                        | ISEN offset                                       | $I_{O} = 0 \text{ A, V}_{ISEN} = 1.2 \text{ V}$ $T_{J} = +25 \text{ °C}$ | -4  | 0    | 4    | μA    |

| V <sub>ISEN</sub>                            | ISEN voltage range                                |                                                                          | 0.7 |      | 2.1  | V     |

| I <sub>LIM H</sub>                           |                                                   | Threshold, cycle-by-<br>cycle                                            |     | 120  |      | А     |

| -51147-11                                    |                                                   | Shutdown counter                                                         |     | 10   |      | Times |

| I <sub>LIM_L</sub>                           | Low-side current limit                            | Threshold, cycle-by-cycle  No fault report                               |     | -50  |      | А     |

| _                                            |                                                   | Off time                                                                 |     | 200  |      | ns    |

# Electrical specifications for BMR511 – Power Conversion (1.8 V out)

$T_{P1}$  = -10 °C to 95 °C,  $V_{I}$  = 5 to 15 V,  $V_{CC}$  = 3.3 V, unless otherwise specified under Conditions.

Typical values given at:  $T_{P1} = +25$  °C,  $V_1 = 12V$ ,  $V_0 = 1.8$  V,  $I_0 = 80$  A,  $f_{sw} = 800$  kHz, 2-phase single rail operation, otherwise specified under Conditions.

Measurements made on Reference board ROA 170 347.

External  $C_{IN}$  = 1 x 270  $\mu$ F/22 m $\Omega$  OSCON + 28 x 10  $\mu$ F ceramic.

External  $C_{OUT}$  = 10 x 470  $\mu$ F/3 m $\Omega$  POSCAP + 356 x 10  $\mu$ F ceramic.

| Char            | acteristics                        | Conditions               | min | typ | max  | Unit  |

|-----------------|------------------------------------|--------------------------|-----|-----|------|-------|

| Vı              | Input supply                       | Continuous operation     | 5   |     | 15   | V     |

| V               |                                    | Peak                     |     |     | 16   | V     |

| Vcc             | Driver and logic supply            |                          | 3.0 | 3.3 | 3.6  | V     |

| Vo              | Output voltage range               |                          | 0.5 |     | 1.8  | V     |

| Voac            | Output ripple & noise              | 20 MHz BW                |     | 3   |      | mVp-p |

| f <sub>SW</sub> | Switching frequency                | T <sub>P1</sub> = +25 °C | 500 | 800 | 1000 | kHz   |

| Сı              | Internal input capacitance         | V <sub>I</sub> = 0 V     |     | 8.8 |      | μF    |

| Со              | Internal output capacitance        | V <sub>O</sub> = 0 V     |     | 0   |      | μF    |

| Lo              | Output inductance                  | I <sub>O</sub> = 0 A     |     | 120 |      | nH    |

|                 |                                    |                          |     |     |      |       |

|                 | Output current, peak               | 2-phase operation        |     |     | 140  | Α     |

|                 | Output correin, peak               | 1-phase operation        |     |     | 70   | Α     |

| lo              | Outrout oursent continuous Note 1  | 2-phase operation        | 0   | 80  |      | Α     |

|                 | Output current, continuous, Note 1 | 1-phase operation        | 0   | 40  |      | А     |

|                 |                                    |                          |     |     |      |       |

| I <sub>IN</sub> | VIN input current                  | Standby, EN = low        |     | 10  |      | μΑ    |

|                 |                                    | 1-phase operation        |     | 20  |      |       |

|                 |                                    | I <sub>O</sub> = 40 A    |     | 38  |      | mA    |

|                 |                                    | 2-phase operation        |     |     |      |       |

| Ivcc            | VCC input current                  | I <sub>O</sub> = 80 A    |     | 71  |      | mA    |

|                 |                                    | Standby,                 |     |     |      |       |

|                 |                                    | · ·                      |     | 3   |      | mA    |

|                 |                                    | PWM1 = PWM2 = Iow        |     |     |      |       |

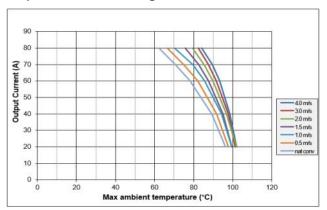

Note 1: The maximum continuous output current will also be limited by the thermal conditions.

See derating graphs and section Thermal Considerations.

Vin =5~6V, Vo=1.8V, Io typ=50A

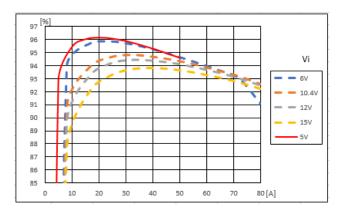

# **Electrical graphs for BMR511**

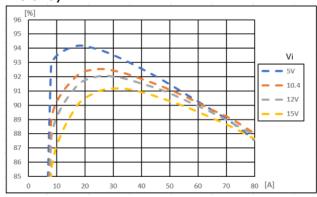

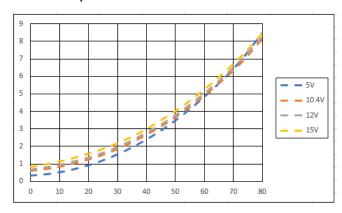

### $V_{out} = 1.8 V$

### **Efficiency**

Driver losses excluded, 2 phases, fsw=800 kHz

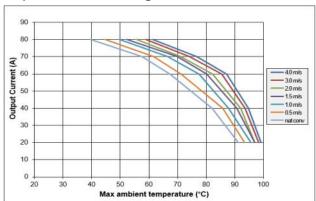

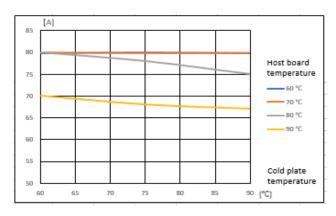

### **Output Current Derating-wind tunnel**

Available load current vs. ambient air temperature and air flow at  $V_{\text{I}}$ = 12V.

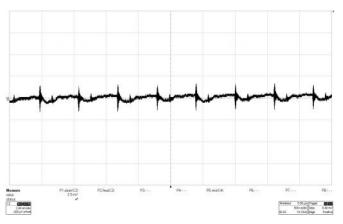

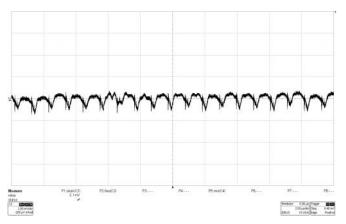

### **Output ripple**

$V_I$  = 12 V,  $I_O$  = 80 A, Scale: 2 mV/div, 0.5  $\mu s/div$ , 20 MHz BW.  $C_{OUT}$  = 10 x 470  $\mu F/3$  mQ POSCAP + 365 x 10  $\mu F$  ceramic.

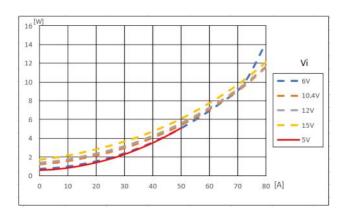

### **Power dissipation**

Driver losses excluded, 2 phases, fsw= 800 kHz

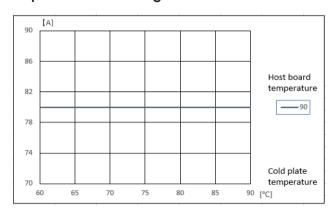

### **Output Current Derating-cold wall**

Thermal interface gap pad 1 mm, 8 W/mK.  $V_i$ = 12V.

# Electrical specifications for BMR511 – Power Conversion (0.75 V out)

$T_{P1}$  = -10 °C to 95 °C,  $V_{I}$  = 5 to 15 V,  $V_{CC}$  = 3.3 V, unless otherwise specified under Conditions.

Typical values given at:  $T_{P1} = +25$  °C,  $V_1 = 12V$ ,  $V_0 = 0.75V$ ,  $I_0 = 80$  A,  $f_{sw} = 450$  kHz, 2-phase single rail operation, otherwise specified under Conditions.

Measurements made on Reference board ROA 170 347.

External  $C_{IN}$  = 1 x 270  $\mu$ F/22 m $\Omega$  OSCON + 28 x 10  $\mu$ F ceramic.

External  $C_{OUT}$  = 10 x 470  $\mu$ F/3 m $\Omega$  POSCAP + 356 x 10  $\mu$ F ceramic.

| Char            | acteristics                        | Conditions               | min | typ  | max  | Unit  |

|-----------------|------------------------------------|--------------------------|-----|------|------|-------|

| Vı              | Input supply                       | Continuous operation     | 5   |      | 15   | V     |

| ٧١              |                                    | Peak                     |     |      | 16   | V     |

| Vcc             | Driver and logic supply            |                          | 3.0 | 3.3  | 3.6  | V     |

| Vo              | Output voltage range               |                          | 0.5 | 0.75 | 1.8  | V     |

| Voac            | Output ripple & noise              | 20 MHz BW                |     | 3    |      | mVp-p |

| fsw             | Switching frequency                | T <sub>P1</sub> = +25 °C | 400 | 450  | 1000 | kHz   |

| Сі              | Internal input capacitance         | V <sub>I</sub> = 0 V     |     | 8.8  |      | μF    |

| Со              | Internal output capacitance        | V <sub>O</sub> = 0 V     |     | 0    |      | μF    |

| Lo              | Output inductance                  | I <sub>O</sub> = 0 A     |     | 120  |      | nH    |

|                 |                                    |                          |     |      |      |       |

|                 | Output current, peak               | 2-phase operation        |     |      | 140  | Α     |

|                 | Output correcti, peak              | 1-phase operation        |     |      | 70   | А     |

| lo              | Output ourselt continues Note 2    | 2-phase operation        | 0   | 80   |      | А     |

|                 | Output current, continuous, Note 2 | 1-phase operation        | 0   | 40   |      | А     |

|                 |                                    |                          |     |      |      |       |

| I <sub>IN</sub> | VIN input current                  | Standby, EN = low        |     | 10   |      | μΑ    |

|                 |                                    | 1-phase operation        |     | 20   |      | 4     |

|                 |                                    | I <sub>O</sub> = 40 A    |     | 38   |      | mA    |

|                 |                                    | 2-phase operation        |     |      |      |       |

| Ivcc            | VCC input current                  | I <sub>O</sub> = 80 A    |     | 71   |      | mA    |

|                 |                                    | Standby,                 |     |      |      |       |

|                 |                                    | ,                        |     | 3    |      | mA    |

|                 |                                    | PWM1 = PWM2 = low        |     |      |      |       |

Note 2: The maximum continuous output current will also be limited by the thermal conditions.

See derating graphs and section Thermal Considerations.

1/28701-BMR 511 Rev B 2023-06-16 8

# **Electrical graphs for BMR511**

### $V_{out} = 0.75 V$

### **Efficiency**

Driver losses excluded, 2 phases, fsw=450 kHz

### **Output Current Derating-wind tunnel**

Available load current vs. ambient air temperature and air flow at  $V_{I=12V}$

### **Output ripple**

$V_I$  = 12 V,  $I_O$  = 80 A, Scale: 2 mV/div, 2  $\mu s/div$ , 20 MHz BW.  $C_{OUT}$  = 10 x 470  $\mu F/3$  mQ POSCAP + 365 x 10  $\mu F$  ceramic.

### **Power dissipation**

Driver losses excluded, 2 phases, fsw= 450 kHz

### **Output Current Derating-cold wall**

Thermal interface gap pad 1 mm, 8 W/mK.  $V_1$ = 12V.

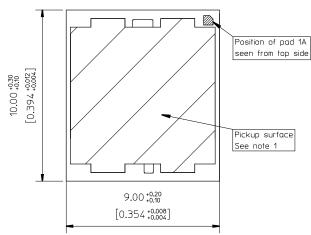

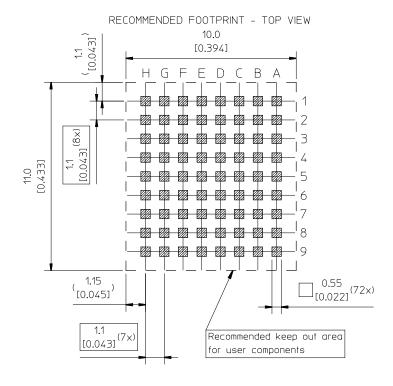

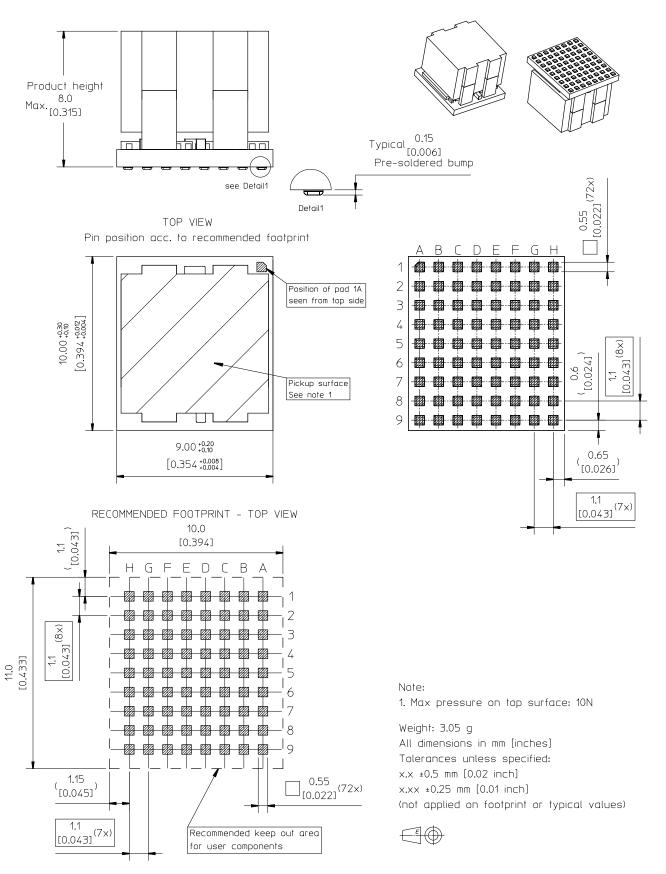

### Part 2: Mechanical information

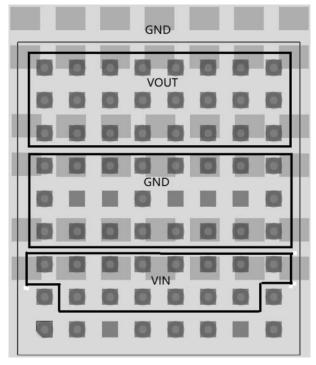

### **BMR511:** Surface Mount Version

$\begin{tabular}{ll} TOP \ VIEW \\ Pin \ position \ acc. \ to \ recommended \ footprint \\ \end{tabular}$

#### Note:

1. Max pressure on top surface: 10N

Weight: 3.05 g

All dimensions in mm [inches]

Tolerances unless specified:

x.x ±0.5 mm [0.02 inch]

x.xx ±0.25 mm [0.01 inch]

(not applied on footprint or typical values)

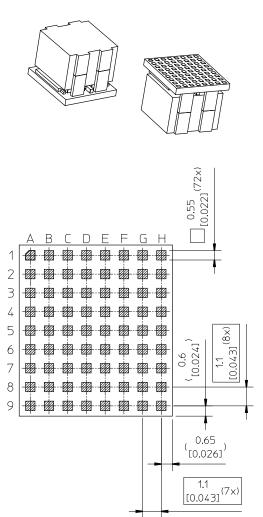

Part 2: Mechanical information

### BMR511: Surface Mount Version with solder bumps

# Connections

### Part 2: Mechanical information

| Н    | G   | F     | Ε         | D    | $\subset$ | В     | А     |   |

|------|-----|-------|-----------|------|-----------|-------|-------|---|

| PWM1 | EN1 | TSEN1 | ISEN1     | PWM2 | EN2       | TSEN2 | ISEN2 | 1 |

| VCC5 |     |       |           |      |           |       | VCC33 | 2 |

|      |     |       | $\square$ |      |           |       |       | 3 |

|      |     |       |           |      |           |       |       | 4 |

|      |     |       |           |      |           |       |       | 5 |

|      |     |       |           | ND D |           |       |       | 6 |

|      |     |       |           |      |           |       |       | 7 |

|      | VO  |       |           |      |           | JT2   |       | 8 |

|      |     |       |           |      |           |       |       | 9 |

### Pin layout, top view

| Pin                     | Designation | Туре   | Function                                                                                                         |

|-------------------------|-------------|--------|------------------------------------------------------------------------------------------------------------------|

| A1                      | ISEN2       | Output | Current sense output, phase 2. Use external resistor to adjust the voltage proportional to the inductor current  |

| A2                      | VCC33       | input  | Driver and internal circuitry supply. Connect to +3.3 V.                                                         |

| B1                      | TSEN2       | Output | Temperature sense and fault reporting, phase 2.                                                                  |

| C1                      | EN2         | Input  | Active high enable input, phase 2                                                                                |

| DI                      | PWM2        | Input  | Pulse-width modulation input, phase 2. The PWM2 signal shall be 180° phase shifted compared to the PWM1 signal   |

| E1                      | ISEN1       | Output | Current sense output, phase 1. Use external resistor to adjust the voltage proportional to the inductor current  |

| F1                      | TSEN1       | Output | Temperature sense and fault reporting, phase 1.                                                                  |

| G1                      | EN1         | Input  | Active high enable input, phase 1.                                                                               |

| Н1                      | PWM1        | Input  | Pulse-width modulation input, phase 1. The PWM1 signal shall be 180° phase shifted compared to the PWM2 signal . |

| H2                      | VCC5        | NC     | No connection.                                                                                                   |

| B2-G2, A3-H3            | VIN         | Power  | Input voltage .                                                                                                  |

| A4-H4, A5-H5,<br>A6-H6  | GND         | Power  | Power ground and digital ground .                                                                                |

| A7-D7, A8- D8,<br>A9-D9 | VOUT2       | Power  | Output voltage, phase 2                                                                                          |

| E7-H7, E8-H8,<br>E9-H9  | VOUT1       | Power  | Output voltage, phase 1                                                                                          |

### Part 3: Thermal considerations

#### **Thermal Consideration**

#### General

The product is designed with inductor on top. Cooling is mainly achieved by conduction to the host board and convection which is dependent on the airflow across the product. Increased airflow enhances the cooling of the product.

The Output Current Derating graph found in the Electrical Specification section provides the available output current versus Max. ambient temperature, and output current versus cold plate temperature and host board temperature.

### Test Setup - Wind tunnel

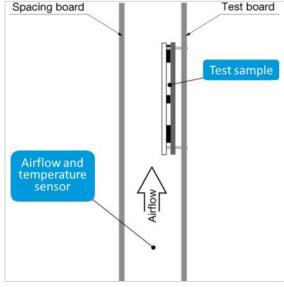

The product is tested on a 254 x 254 mm, 35  $\mu$ m (1 oz), 8 layer test board mounted vertically in a wind tunnel with a cross section of 608 x 203 mm. Distances between the tested device and the top space board are 12 mm.

### Test Setup – Cold Plate

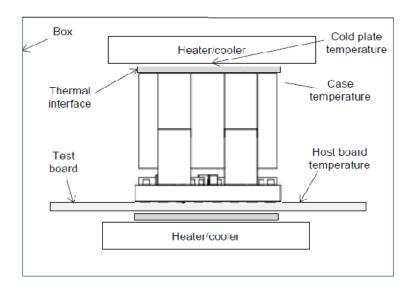

The product is tested in a box with two heater/coolers; one as a cold plate to control the temperature at the top of the module, another on the bottom side of the test board to control the host board temperature. The test board used is 254 x 254 mm in size with 1.6 mm thickness and 8 layers of 1 oz.

Picture: test setup — Cold plate

### **Definition of Product Operating Temperature**

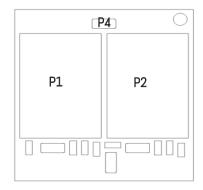

The temperature at positions P1-P4 should not exceed the maximum temperatures in the table below. The number of measurement points may vary with different thermal design and topology. Temperature above specified maximum measured at the specified position is not allowed and may cause permanent damage.

1/28701-BMR 511 Rev B 2023-06-16 13

### Part 3: Thermal considerations

| Position | Description                               | Max temperature        |

|----------|-------------------------------------------|------------------------|

| P1       | Power switch case phase 1 reference point | T <sub>P1</sub> =125°C |

| P2       | Power switch case phase 2                 | T <sub>P2</sub> =125°C |

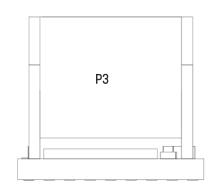

| P3       | M1, Inductor core                         | T <sub>P3</sub> =125°C |

| P4       | capacitors                                | T <sub>P4</sub> =105°C |

Top view (inductor removed)

Side view

# Part 4: PCB layout considerations

### **PCB Layout Consideration**

- 1. The radiated EMI performance of the product will depend on the PCB layout and ground layer design. A ground plane shall be used, to increase the stray capacitance in the PCB and improve the high frequency EMC performance. The ground plane shall connect to the GND pins of the devices and the equipment ground or chassis.

- 2. For a multiphase rail including several power modules, layout should be as symmetrical as possible in order to help balance the current between devices.

- 3. If possible, use planes on several layers to carry VI, VO and ground. There should be a large number of vias close to the VIN, VOUT and GND pins to lower input and output impedances and improve heat spreading between the product and the host board.

- 4. Care should be taken in the routing of the ISEN and TSEN connections. The routing should be along a GND plane and should avoid areas of switching signals or high electric or magnetic fields, e.g. keep away from PWM signals.

- 5. The external input capacitors, CI\_EXT, shall be placed as close to the input pins as possible and with low impedance connections, e.g. using via stitching around capacitors' terminals. See AN323 for more details.

- 6. The external output capacitors, CO\_EXT, should be placed close to the output pins to handle the output current ripple, and close to the load to handle the load transients. See AN321 for more details. Low impedance connections must be used, e.g. via stitching around capacitors' terminals.

Below picture shows a layout example where the module is mounted on the top side of the PCB and 7 pcs 0603 input capacitors and 14 pcs 0603 output capacitors are placed on the bottom side of the PCB, providing a short connection to the VIN, VOUT and GND pins through vias in module pads.

Layout example: Input and output capacitance placement close to the module (top view).

1/28701-BMR 511 Rev B 2023-06-16 15

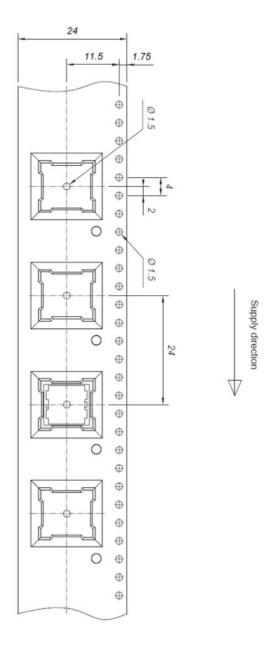

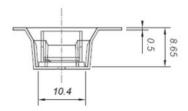

# Part 5: Packaging

# **Packaging information**

| C option:                    |                                                 |

|------------------------------|-------------------------------------------------|

|                              |                                                 |

| Material                     | Antistatic polyphenylene ester (PPE)            |

| Surface<br>resistance        | 10 <sup>5</sup> < ohm/square < 10 <sup>11</sup> |

| Bakeabilty                   | The tape is not bakeable                        |

| Tape width, W                | 24 mm [0.95 inch]                               |

| Pocket pitch, P <sub>1</sub> | 24 mm [0.95 inch]                               |

| Pocket depth, K <sub>0</sub> | 8.65 mm [0.34 inch]                             |

| Reel diameter                | 330 mm [13.0 inch]                              |

| Reel capacity                | 300 products /reel                              |

| Reel weight                  | 1400 g/full reel                                |

# Part 6: Revision history

### **Revision table**

| Revision number | revision change | date      | revisor  |

|-----------------|-----------------|-----------|----------|

| Rev. A          | New document    | 2023/6/15 | JIDDIYAN |

| Rev. B          | Spell check     | 2023/6/15 | KARTWAER |

|                 |                 |           |          |

|                 |                 |           |          |

### © Flex Power Modules 2023

The information and specifications in this technical specification is believed to be correct at the time of publication. However, no liability is accepted for inaccuracies, printing errors or for any consequences thereof. Flex reserves the right to change the contents of this technical specification at any time without prior notice.

### TECHNICAL REFERENCE DOCUMENT: GENERAL INFORMATION

### Compatiblity with RoHS requirements

The products are compatible with the relevant clauses and requirements of the *RoHS directive 2011/65/EU* and 2015/863 have a maximum concentration value of 0.1% by weight in homogeneous materials for lead, mercury, hexavalent chromium, PBB, PBDE, DEHP, BBP, DBP, DIBP and of 0.01% by weight in homogeneous materials for cadmium.

Exemptions in the RoHS directive utilized in Flex Power Modules products are found in the <u>Statement of Compliance document</u>.

Flex Power Modules fulfills and will continuously fulfill all its obligations under regulation (EC) No 1907/2006 concerning the registration, evaluation, authorization and restriction of chemicals (REACH) as they enter into force and is through product materials declarations preparing for the obligations to communicate information on substances in the products.

### **Quality statement**

The products are designed and manufactured in an industrial environment where quality systems and methods like <u>ISO 9001</u>, <u>ISO 14001</u>, <u>ISO 45001</u>, Six *Sigma*, and *SPC* are intensively in use to boost the continuous improvements strategy. Infant mortality or early failures in the products are screened out and they are subjected to an ATE-based final test. Conservative design rules, design reviews and product qualifications, plus the high competence of an engaged workforce, contribute to the high quality of the products.

### Warranty

Warranty period and conditions are defined in Flex Power Modules' General Terms and Conditions of Sales.

### **Limitation of Liability**

Flex Power Modules does not make any other warranties, expressed or implied including any warranty of merchantability or fitness for a particular purpose (including, but not limited to, use in life support applications, where malfunctions of product can cause injury to a person's health or life).

2/28701-BMR 511 REV B 2023/6/16

# **Product qualification specifications**

| Characteristics                                             |                                                         |                                                        |                                                        |

|-------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| External visual inspection                                  | IPC-A-610                                               |                                                        |                                                        |

| Temperature shock test (Temperature cycling)                | IEC 60068-2-14 Na                                       | Temperature range Number of cycles Dwell/transfer time | -40 to 125°C<br>700<br>15 min/0-1 min                  |

| Cold (in operation)                                         | IEC 60068-2-1 Ad                                        | Temperature T <sub>A</sub> Duration                    | -45°C<br>72 hr                                         |

| Damp heat                                                   | IEC 60068-2-67 Cy                                       | Temperature<br>Humidity<br>Duration                    | 85°C<br>85% RH<br>1000 hr                              |

| Dry heat                                                    | IEC 60068-2-2 Bd                                        | Temperature Duration                                   | 125°C<br>1000 hr                                       |

| Electrostatic discharge susceptibility                      | IEC 61340-3-1, JESD 22-A114 IEC 61340-3-2, JESD 22-A115 | Human body model (HBM)  Machine Model (MM)             | Class 2, 2000 V<br>Class 3, 200 V                      |

| Immersion in cleaning solvents                              | IEC 60068-2-45 XA, method 2                             | Water Fluxcleaner Isopropyl alcohol                    | 55°C<br>23° C<br>35°C                                  |

| Mechanical shock                                            | IEC 60068-2-27 Ea                                       | Peak acceleration Duration                             | 100 g<br>6 ms                                          |

| Moisture classification and reflow sensitivity <sup>1</sup> | J-STD-020E                                              | Level 3 (Pb Free)                                      | 245°C                                                  |

| Operational Life test Rapid<br>Temp.                        | MIL-STD-202G, method 108A                               | Duration                                               | 1000 hr                                                |

| Robustness of terminations                                  | IEC 60068-2-21 Test Ue1                                 | Surface mount products                                 | All leads                                              |

| Solderability (surface mount)                               | IEC 60068-2-58 test T <sub>d</sub>                      | Preconditioning Temperature, Pb-free                   | Steam ageing<br>245°C                                  |

| Vibration, broad band random                                | IEC 60068-2-64 Fh, method 1                             | Frequency Spectral density Duration                    | 10 to 500 Hz<br>0.07 g²/Hz<br>10 min in each direction |

Note 1: only for products intended for reflow soldering (surface mount products & pin-in paste products)

2/28701-BMR 511 REV B 2023/6/16 2

### TECHNICAL REFERENCE DOCUMENT: DESIGN & APPLICATION GUIDELINES

### **Operating Information**

BMR 511 is a two-phase non-isolated high-efficiency small footprint step-down power block. It includes drivers, MOSFETs, output inductors and sensing circuitry for output currents and junction temperatures. Further, it includes over-current and over-temperature protection functions with fault reporting. The product has two independent outputs, which can be used separately (dual rail) or in parallel (single rail dual phase). Several products can be paralleled for multiphase operation.

### Input and Output Impedance

The impedance of both the input source and the load will interact with the impedance of the product. It is important that the input source has low characteristic impedance. If the input voltage source contains significant inductance, the addition of a capacitor with low ESR at the input of the product will ensure stable operation.

### **External Input Capacitors**

For most applications non-tantalum capacitors are preferred due to the robustness of such capacitors to accommodate high inrush currents of systems being powered from very low impedance sources. It is recommended to use a combination of ceramic capacitors and low-ESR electrolytic/polymer bulk capacitors. The low ESR of ceramic capacitors effectively limits the input ripple voltage level, while the bulk capacitance minimizes deviations in the input voltage during large load transients.

It is recommended to use at least 70  $\mu$ F ceramic external input capacitors for each module, placed closed to input pins and with low impedance connections to the VIN and GND pins to be effective. See application note AN323 for further guidelines on how to choose and apply input capacitors.

#### **External Output Capacitors**

The output capacitor requirement depends on two considerations: output ripple voltage and load transient response. To achieve low ripple voltage, the output capacitor bank must have a low ESR value, which is achieved with ceramic output capacitors. A low ESR value is critical also for a small output voltage deviation during load transients. Designs with smaller load transients can use fewer capacitors and designs with more dynamic load content will require more load capacitors to minimize output voltage deviation.

It is recommended to place at least  $140 \, \mu F$  ceramic capacitors close to each product, since it has no internal output capacitance. In addition, low ESR ceramic and low ESR electrolytic/polymer capacitors shall be placed as close to the load as possible, using several capacitors in parallel to lower the effective ESR. It is important to use low resistance and low inductance PCB layouts for capacitance to be effective.

See application note AN321 for further guidelines on how to choose and apply output capacitors.

3/28701-BMR 511 Rev A 2023/6/15 1

### TECHNICAL REFERENCE DOCUMENT: DESIGN & APPLICATION GUIDELINES

#### **Enable**

When the voltages at VIN and VCC pins are sufficiently high and the EN pin is high, operation begins. There are seperated EN pins for each phase.

### Pulse-Width Modulation (PWM)

The pulse-width modulation input pins are capable of tri-state input. When the PWM input is high, the high-side MOSFET is turned on and the low-side MOSFET is turned off. When the PWM input is low, the high-side MOSFET is turned off and the low-side MOSFET is turned on. If the PWM input is floated, it will force the PWM into tri-state.

When the PWM input signal is within the tri-state threshold window for a typical 40 ns, the high-side MOSFET turns off immediately, and the low-side MOSFET enters diode emulation mode, which is on until zero-current detection.

The tri-state PWM input can come from a forced mid-voltage PWM signal or made by floating the PWM input. The internal current source charges the signal to a middle voltage.

When operating both phases of the product, PWM1 and PWM2 pulses shall be 180° shifted.

### **Diode Emulation Mode**

In diode emulation mode, when PWM is in a tri-state input, the low side MOSFET is turned on whenever the inductor current is positive. The low side MOSFET turns off if the inductor current is negative or after the inductor current crosses the zero current.

#### **Current Sense**

The ISEN pins are bidirectional current source outputs proportional to the inductor current of each phase. The gain is  $5 \,\mu\text{A/A}$ . An external resistor must be used to program the voltage gain proportional to the inductor current, if needed.

The ISEN outputs have two states. In disable mode (EN = low), the current sense circuit is disabled and the ISEN outputs are in the high impedance state.

| EN   | ISEN   |  |

|------|--------|--|

| High | Active |  |

| Low  | Hi-Z   |  |

The voltage of the ISEN pins must be within the specified voltage range to achieve an accurate current reporting. In general, there is a resistor, RIOUT, connected from ISEN to a reference voltage, VCM, that can sink small currents to provide enough voltage level to meet the required operating voltage range. Proper VCM and RIOUT values can be determined by the equation:

$0.7 \text{ V} < (I_{ISEN} \times R_{IOUT}) + V_{CM} < 2.1 \text{ V}$

### TECHNICAL REFERENCE DOCUMENT: DESIGN & APPLICATION GUIDELINES

The current sense outputs can be used by the controller to monitor the output current accurately. The cycle -by-cycle current information from the ISEN pins can be used for phase- current balancing, over-current protection, and voltage positioning (output voltage droop).

#### **Current Limit**

When high side over-current is detected, the high side MOSFET turns off for that PWM cycle. If there are ten consecutive cycles of a high side current limit event, the high side MOSFET latches off, TSEN pulls high to VCC, and the low side MOSFET turns on until zero current detection. Toggle EN or recycle VIN or VCC to release the latch and restart operation.

When the low side under-current is detected (negative current) the low side MOSFET is turned off and the high side MOSFET is turned on for 200 ns to limit the negative current cycle by cycle. The low side negative current limit will not trigger a fault report.

### Temperature Sense with Fault Indicator

The TSEN pins have two functions:

- 1. Junction temperature sense.

- 2. Fault detection.

The voltage at the TSEN pin is proportional to the junction temperature whenever VIN and VCC is higher than their UVLO thresholds. The gain is 8 mV/°C and has an 800 mV offset at 25 °C. Examples:

$$V_{TSEN} = 0.8 V @ TJ = 25 °C$$

$V_{TSEN} = 1.6 V @ TJ = 125 °C$

When any fault occurs, TSEN is pulled to the VCC voltage to report the fault event, regardless of the current junction temperature. 200 ns after the fault has occurred, the PWM impedance changes accordingly to indicate the fault type:

| Fault Type                        | PWM Impedance |  |

|-----------------------------------|---------------|--|

| Over-current limit protection     | 10 kΩ to GND  |  |

| Over-temperature limit protection | 20 kΩ to GND  |  |

| Internal short protection         | 1 kΩ to VCC   |  |

For multiphase operation, connect TSEN of each phase together to report the highest junction temperature. It is recommended to add a filter to the TSEN signal. See Application Example for typical component values to use.

#### **Temperature Limit**

When the over-temperature threshold is exceeded, the high side MOSFET latches off, TSEN pulls high to VCC, and the low side MOSFET turns on until zero current detection. Toggle EN or recycle VIN or VCC to release the latch and restart operation.

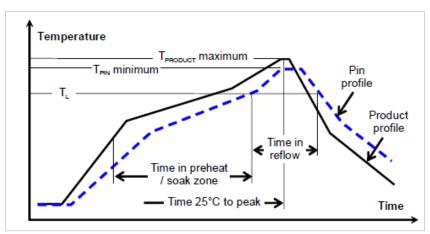

### TECHNICAL REFERENCE DOCUMENT: SOLDERING

### Soldering Information — Surface mounting

Products intended for surface mount assembly are qualified for use in a Pb-free forced convection or vapor phase reflow soldering process.

The surface mount product is intended for forced convection or vapor phase reflow soldering in Pb-free processes.

The reflow profile should be optimised to avoid excessive heating of the product. It is recommended to have a sufficiently extended preheat time to ensure an even temperature across the host PCB and it is also recommended to minimize the time in reflow.

A no-clean flux is recommended to avoid entrapment of cleaning fluids in cavities inside the product or between the product and the host board, since cleaning residues may affect long time reliability and isolation voltage.

T<sub>L</sub> is the typical solder melting (liquidous) temperature

T<sub>product</sub> is measured on the power module's hotspot

T<sub>pin</sub> is measured on the power module output power pins' solder joints at the customer board

| General relfow process specification         |                  | Pb-free, SAC305 |

|----------------------------------------------|------------------|-----------------|

| Average ramp-up rate (T <sub>product</sub> ) |                  | 3 °C/s max      |

| Typical solder melting temp.                 | TL               | 221° C          |

| Min/Max. reflow time above T <sub>L</sub>    | Tpin             | 60 –150 s       |

| Min. pin temp.                               | T <sub>pin</sub> | 235 °C          |

| Peak product temp.                           | Tproduct         | 245 °C          |

| Average ramp-down (T <sub>product</sub> )    |                  | 6°C/s max       |

| Max. time 25° C to peak                      |                  | 8 minutes       |

Typical soldering profile

#### Pb-free solder classification

For Pb-free solder processes, the product is qualified for MSL 3 according to IPC/JEDEC standard J-STD-020E.

### Products reflow processes - Lead-free (Pb-free) solder processes

For Pb-free solder processes, a pin temperature (T<sub>MIN</sub>) in excess of the solder melting temperature (T<sub>L</sub>, 217 to 221 °C for SnAgCu solder alloys) for more than 30 seconds and a peak temperature of 235 °C on all solder joints is recommended to ensure a reliable solder joint

During reflow T<sub>PRODUCT</sub> must not exceed 245 °C at any time.

### **Dry Pack Information**

The products are delivered in standard moisture barrier bags according to IPC/JEDEC standard J-STD-033 (Handling, packing, shipping and use of moisture/reflow sensitivity surface mount devices).

Using products in high temperature Pb-free soldering processes requires dry pack storage and handling. In case the products have been stored in an uncontrolled environment and no longer can be considered dry, the products must be baked according to J-STD-033.

### Surface Mount Assembly and Repair

#### **Assembly**

This product is **not** recommended for assembly on the bottom side of a customer board. If such an assembly is attempted, components may fall off the product during the second reflow process.

#### Repair

For a successful repair (removal and replacement) of a LGA product, a dedicated rework system should be used. The rework system should preferably utilize a reflow station and a bottom side heater might also be needed for the operation.

4/28701-BMR 511 REV A 2023/6/15 2

### TECHNICAL REFERENCE DOCUMENT: SAFETY

### Safety specifications

Flex Power Modules' DC/DC converters and DC/DC regulators are designed in accordance with the safety standards IEC 62368-1, EN 62368-1 and UL 62368-1 Audio/video, information and communication technology equipment - Part 1: Safety requirements

IEC/EN/UL 62368-1 contains requirements to prevent injury or damage due to the following hazards:

- Electrical shock

- Electrically-caused fire

- Injury caused by hazardous substances

- Mechanically-caused injury

- Skin burn

- Radiation-caused injury

On-board DC/DC converters, Power Interface Modules and DC/DC regulators are defined as component power supplies. As components they cannot fully comply with the provisions of any safety requirements without "conditions of acceptability". Clearance between conductors and between conductive parts of the component power supply and conductors on the board in the final product must meet the applicable safety requirements. Certain conditions of acceptability apply for component power supplies with limited stand-off (please refer to Technical Specification under Mechanical Information for further information). It is the responsibility of the installer to ensure that the final product housing these components complies with the requirements of all applicable safety standards and regulations for the final product.

Component power supplies for general use shall comply with the requirements in IEC/EN/UL 62368-1. Product related standards, e.g. IEEE 802.3af Power over Ethernet, and ETS-300132-2 Power interface at the input to telecom equipment, operated by direct current (dc) are based on IEC/EN/UL 62368-1 with regards to safety.

All Flex Power Modules' DC/DC converters, Power Interface Modules and DC/DC regulators are recognized and certified in accordance with IEC/EN/UL 62368-1. The flammability rating for all construction parts of the products meet requirements for V-0 class material according to IEC 62368-11-10 Fire hazard testing, test flames – 50 W horizontal and vertical flame test methods.

## Non-isolated DC/DC regulators

The DC/DC regulator output is ES1 energy source if the input source meets the requirements for ES1 according to IEC/EN/UL 62368-1.

5/28701-BMR 511 Rev A 2023/6/15