#### TECHNICAL REFERENCE DOCUMENT: DESIGN & APPLICATION GUIDELINES

#### **OPERATING INFORMATION: COMMON FEATURES**

The features listed in the following pages are common to DC/DC converters.

### Turn on and off input voltage

The product monitors the input voltage and will turn on and turn off at configured thresholds (see Technical Specification: part 1 - Electrical Specification). The turn-on input voltage threshold is set higher than the corresponding turn-off threshold. Hence, there is a hysteresis between turn-on and turn-off input voltage levels.

## Input voltage transient

The end-user must secure that the transient voltage will not exceed the value stated in the Technical Specification under Absolute maximum ratings of each product. ETSI TR 100 283 examines the parameters of DC distribution networks and provides guidelines for controlling the transient and reduce its harmful effect.

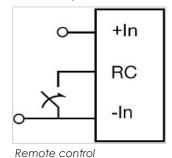

### Remote control (RC)

The products are fitted with a remote control function referenced to the primary negative input connection (-In), with negative logic options available. The RC function allows the product to be turned on/off by an external device like a semiconductor or mechanical switch. The RC pin has an internal pull up resistor.

The external device must provide a minimum required sink current > 1.5 mA to guarantee a voltage not higher than maximum voltage on the RC pin (see Electrical characteristics table). To turn off the product the RC pin should be left open for a minimum time of 150 µs, the same time requirement applies when the product shall turn on. When the RC pin is left open, the voltage generated on the RC pin is max 6 V. The standard product is provided with "negative logic" RC and will be off until the RC pin is connected to the – In. To turn off the product the RC pin should be left open. In situations where it is desired to have the product to power up automatically without the need for control signals or a switch, the RC pin shall be wired directly to –In.

3/28701-BMR 684 Rev A 3/31/2023

### Input and output impedance

The impedance of both the input source and the load will interact with the impedance of the product. It is important that the input source has low characteristic impedance. Minimum recommended external input capacitance is given in the *Technical Specification*. Electrolytic capacitors will be degraded in low temperature. The needed input capacitance in low temperature should be equivalent to the value stated in the Technical Specification at 25°C. The performance in some applications can be enhanced by addition of external capacitance as described under External decoupling capacitors (next paragraph). If the input voltage source contains significant inductance, the addition of a low ESR ceramic capacitor of  $22 - 100 \, \mu F$  capacitor across the input of the product will ensure stable operation. The minimum required capacitance value depends on the output power and the input voltage. The higher output power the higher input capacitance is needed.

### **External decoupling capacitors**

When powering loads with significant dynamic current requirements, the voltage regulation at the point of load can be improved by addition of decoupling capacitors at the load.

The most effective technique is to locate low ESR ceramic and electrolytic capacitors as close to the load as possible, using several parallel capacitors to lower the effective ESR. The ceramic capacitors will handle high-frequency dynamic load changes while the electrolytic capacitors are used to handle low frequency dynamic load changes. It is equally important to use low resistance and low inductance PWB layouts and cabling.

External decoupling capacitors will become part of the product's control loop. The control loop is optimized for a wide range of external capacitance and the maximum recommended value that could be used without any additional analysis is found in the Technical Specification under Electrical specifications. Output filter can be configured and simulated based on the needed control loop and transient response.

For further information please contact your local Flex Power Modules' representative or email us at pm.info@flex.com.

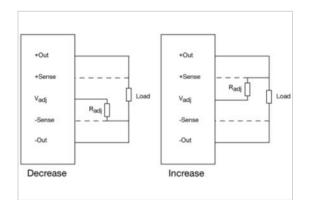

### Output voltage adjust

The output voltage of the product can be reconfigured via PMBus command VOUT\_COMMAND (0x21) or via Vadj pin (pin 6). This can be used when adjusting the output voltage above or below output voltage initial setting, see Electrical specification for adjustment range. When changing the output voltage, the voltage at the output pins must be kept within adjustment range. At increased output voltages, the maximum power rating of the product must remains the same, and the max output current must be decreased correspondingly.

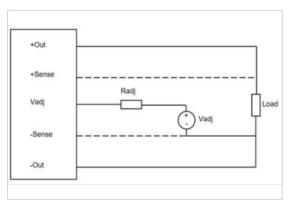

By default, output voltage is adjusted via Vadj pin (pin 6). It is possible to change output voltage either by using passive components or active (dependent source).

If using a resistor to increase the voltage the resistor should be connected between the Vadj pin and +Sense pin. The resistor value of the Output voltage adjust function is according to information given under the Output section for the respective product. To decrease the output voltage, the resistor should be connected between the Vadj pin and –Sense pin. For active adjust, the source and adjust resistor should be connected between the Vadj pin and –Sense pin.

To enable output voltage adjust via PMBus, re-configure PMBus command MFR\_SELECT\_VOUT\_COMMAND (0xBD) using Flex Power Designer software.

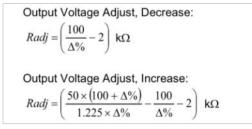

Passive adjust

Passive adjust equation

Active adjust

$$Vadj = \left(1.225 + (Radj + 2) \times 1.225 \times \frac{Vdesired - 50}{50}\right)$$

Active adjust equation

# Margin up and down control

These controls allow the output voltage to be momentarily adjusted, either up or down, by a nominal 10%. The margin high and margin low shall be limited to max and min output voltage, if the nominal output voltage is changed. This provides a convenient method for dynamically testing the operation of the load circuit over its supply margin or range. It can also be used to verify the function of supply voltage supervisors.

The margin up and down levels of the product can easily be re-configured using <u>Flex Power Designer software</u>.

### Soft start power up and soft stop

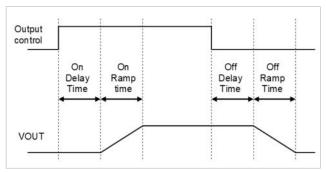

The soft-start and soft-stop control functionality allows the output voltage to ramp-up and ramp-down with defined timing with respect to the control of the output.

The rise time is the time taken for the output to ramp to its target voltage, while the fall time is the time taken for the output to ramp down from its regulation voltage to 0 V. The default rise time is 90 ms. This can be used to control inrush current and manage supply sequencing of multiple controllers.

By default, soft-stop is disabled, and the regulation of output voltage stops immediately when the output is disabled. Soft-stop can be enabled through the PMBus command ON\_OFF\_CONFIG (0x02).

The TON\_DELAY (0x60) sets a delay from when the output is enabled until the output voltage starts to ramp up. The default turn-on delay time is 80ms. When starting by applying input voltage the control circuit bootup time adds approximately an additional 10 ms delay. The TOFF\_DELAY (0x64) sets a delay from when the output is disabled until the output voltage starts to ramp down.

The delay and ramp times can be reconfigured using the PMBus commands TON\_DELAY (0x60), TON\_RISE (0x61), TOFF DELAY (0x64) and TOFF FALL (0x65).

Soft start power up

### Pre-bias start-up

The product has a pre-bias start up functionality and will not sink current during start up if a pre-bias source is present at the output terminals. If the pre-bias voltage is lower than the target value set in VOUT\_COMMAND (0x21), the product will ramp up to the target value. If the pre-bias voltage is higher than the target value set in VOUT\_COMMAND (0x21), the product will ramp down to the target value and in this case sink current for a time interval set by the command TOFF\_MAX\_WARN\_LIMIT (0x66).

# Over/under temperature protection (OTP/UTP)

The products are protected from thermal overload by an internal over temperature sensor.

The product will make continuous attempts to start up (non-latching mode) and resume normal operation automatically when the temperature has dropped below the temperature threshold set in command OT\_WARN\_LIMIT (0x51). The OTP and hysteresis of the product can be re-configured using the PMBus interface. The product also has an under-temperature protection. The OTP and UTP fault limit and fault response can be configured via the PMBus.

Note: using the fault response "continue without interruption" may cause permanent damage to the product.

### Input over/under voltage protection

The product can be protected from high input voltage and low input voltage by a pre-configured value with a response time of 70µs. The over/under-voltage fault level and fault response is easily configured using Flex Power Designer software.

For more information, see Technical Reference Document: PMBus.

# **Output Over Voltage Protection (OVP)**

The product includes over voltage limiting circuitry for protection of the load. If the output voltage exceeds the OVP limit, the product will shutdown and automatic restart (hiccup mode).

The OVP fault level and fault response can be configured via the PMBus interface For more information, see *Technical Reference Document: PMBus*.

# Over current protection (OCP)

The products include current limiting circuitry for protection at continuous overload. For standard configuration the output voltage will shutdown and automatic restart (hiccup mode) for output currents in excess of max output current (max I<sub>o</sub>). The load distribution should be designed for the maximum output short circuit current specified.

The over current protection of the product can be configured via the PMBus interface For more information, see *Technical Reference Document: PMBus*.

### Switching frequency

The product is optimized at the frequency given in the Technical Specification under part 1- Electrical Specification, but can run at lower and higher frequencies through PMBus configuration. The electrical performance can be affected at different frequencies. Please contact your local Flex Power Modules FAE for more details.

#### Address offset

The command FW\_CONFIG\_PMBUS (0xC9) can be configured to utilize different address offset option. There are 2 different address setting options.

- 1. The bit 16 in command 0xC9 is set to 1 to enable PMBus address offset via resistor. The resistor address offset in combination with a value set by PMBus base address, [31:24] in command FW\_CONFIG\_PMBUS (0xC9).

- 2. The bit 16 in command 0xC9 is set to 0 to enable digital PMBus address offset. A PMBus address offset [23:17] is preconfigured in FW\_CONFIG\_PMBUS (0xC9). The digital PMBus address offset in combination with a digital PMBus base address, [31:24] in command FW\_CONFIG\_PMBUS (0xC9). This combination can be chosen if no address resistor is used.

The PMBus-address offset's with resistor value increments the address value following the formula in the PMBus Addressing section of documentation.

### **Feed Forward Capability**

The product has a Feed Forward function implemented that can handle sudden input voltage changes. The output voltage will be regulated during an input transient and will typically stay within 1% when an input transient is applied. The Feed Forward acts on both positive and negative input voltage transients.

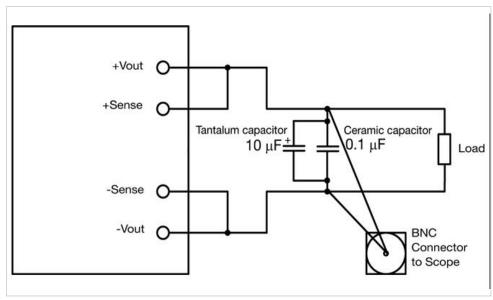

### Output ripple and noise

Output ripple and noise measured according to figure below. See Design Note 022 for detailed information

Output ripple and noise test set-up

### Non-Volatile Memory (NVM)

The product incorporates two Non-Volatile Memory areas for storage of the PMBus command values; the Default NVM and the User NVM. The Default NVM is pre-loaded with Flex factory default values. The Default NVM is write-protected and can be used to restore the Flex factory default values through the command RESTORE\_DEFAULT\_ALL (0x12).

The User NVM is pre-loaded with Flex factory default values. The User NVM is writable and open for customization. The values in NVM are loaded during initialization according to section Initialization Procedure, where after commands can be changed through the PMBus Interface.

The module contains a one-time programmable memory (OTP) used to store configuration settings, which will not be programmed into the device OTP automatically. The STORE\_USER\_ALL(0x15) commands must be used to commit the current settings are transferred from RAM to OTP as device defaults.

### Power good

The power good pin (PG) indicates when the product is ready to provide regulated output voltage to the load. During ramp-up and during a fault condition, PG is held high. By default, PG is asserted low after the output has ramped to setting according to POWER\_GOOD\_ON (0x5E), and de-asserted if the output voltage falls below the setting according to POWER\_GOOD\_OFF (0x5F). These thresholds may be changed using the PMBus commands POWER\_GOOD\_ON (0x5E) and POWER\_GOOD\_OFF (0x5F).

By default, the PG pin is configured as open drain output, and it's internally pulled up to 3.3V. But it is also possible to set the output in push/pull mode by the command MFR\_MULTI\_PIN\_CONFIG (0xF9).

The polarity is by default configured to active low, the polarity of PG can be set to active high using bit [39] in the command FW\_CONFIG\_PMBUS (0xC9):

bit[39] = 0 (active low) bit[39] = 1 (active high)

The product provides a Power Good flag in the Status Word register that indicates the output voltage is within a specified tolerance of its target level and no-fault condition exists. It is not recommended to use push-pull when paralleling PG- pins.

For more information, see Technical Reference Document: PMBus.

#### **POWER MANAGEMENT**

#### **PMBUS** overview

This product is equipped with a PMBus interface. The product incorporates a wide range of readable and configurable power management features that are simple to implement with a minimum of external components. Additionally, the product includes protection features that continuously safeguard the load from damage due to unexpected system faults. A fault is also shown as an alert on the SALERT pin. The following product parameters can continuously be monitored by a host: Input voltage, output voltage/current, duty cycle and internal temperature.

The product is delivered with a default configuration suitable for a wide range operation in terms of input voltage, output voltage, and load. The configuration is stored in an internal Non-Volatile Memory (NVM). All power management functions can be reconfigured using the PMBus interface.

Throughout this document, different PMBus commands are referenced. The Flex Power Designer software suite can be used to configure and monitor this product via the PMBus interface. More information is found on our website.

#### **SMBus interface**

This product provides a PMBus digital interface that enables the user to configure many aspects of the device operation as well as to monitor the input and output voltages, output current and device temperature. The product can be used with any standard two-wire I<sup>2</sup>C (master must allow for clock stretching) or SMBus host device. In addition, the product is compatible with PMBus version 1.3 and includes an SALERT line to help mitigate bandwidth limitations related to continuous fault monitoring. The product supports 100 kHz and 400 kHz bus clock frequency only. The PMBus signals, SCL, SDA and SALERT require passive pull-up resistors as stated in the SMBus Specification. Pull-up resistors are required to guarantee the rise time as follows:

$$\tau = R_p C_p \le 1us$$

Eq. 7

where  $R_p$  is the pull-up resistor value and  $C_p$  is the bus load. The maximum allowed bus load is 400 pF. The pull-up resistor should be tied to an external supply between 2.7 to 3.8 V, which should be present prior to or during power-up. If the proper power supply is not available, voltage dividers may be applied. Note that in this case, the resistance in the equation above corresponds to parallel connection of the resistors forming the voltage divider.

It is recommended to always use PEC (Packet Error Check) when communicating via PMBus.

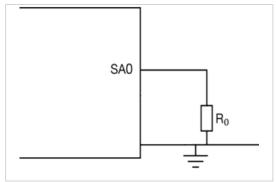

#### PMBus addressing

Hard-wiring PMBus addresses is programmed by connecting SA0 pin to ground with address resistor. SA1 pin has no internal electrical properties and shall not be used. The following table show recommended resistor values (series E96, 1% tolerance resistors suggested).

Schematic of connection address resistor

| R <sub>SA0</sub> [kΩ] | Address offset<br>(dec) | Calculated PMBus<br>address (hex) with base<br>address = 10 (dec) | Valid PMBus address<br>(hex) with base address =<br>10 (dec) |

|-----------------------|-------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|

| 10                    | 0                       | 10                                                                | 0x0A                                                         |

| 15.4                  | 1                       | 11                                                                | OxOB                                                         |

| 23.7                  | 2                       | 12                                                                | 0x7E                                                         |

| 36.5                  | 3                       | 13                                                                | 0x0D                                                         |

| 54.9                  | 4                       | 14                                                                | 0x0E                                                         |

| 84.5                  | 5                       | 15                                                                | 0x0F                                                         |

| 130                   | 6                       | 16                                                                | 0x7E                                                         |

| 200                   | 7                       | 17                                                                | 0x11                                                         |

PMBus base address value is configured via PMBus command 0xC9. The default base address is 0x00.

The allowed range of the PMBus address is: 1-126 excluding 12 and 16. When the calculated PMBus address falls outside the allowed range address 126 is assigned instead. When SAO pin is left open, PMBus address offset is 07(dec).

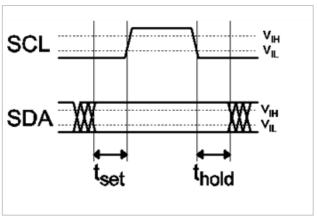

### **I2C/SMBus timing**

The setup time, t<sub>set</sub>, is the time data, SDA, must be stable before the rising edge of the clock signal, SCL. The hold time t<sub>hold</sub>, is the time data, SDA, must be stable after the rising edge of the clock signal, SCL. If these times are violated incorrect data may be captured or meta-stability may occur and the bus communication may fail. All standard SMBus protocols must be followed, including clock stretching. This product supports the BUSY flag in the status commands to indicate product being too busy for SMBus response. A bus-free time delay between every SMBus transmission (between every stop & start condition) must occur. Refer to the SMBus specification, for SMBus electrical and timing requirements.

Note that an additional delay of 5 ms has to be inserted in case of storing the RAM content into the internal non-volatile memory.

Set-up and hold timing diagramm

### Monitoring via PMBus

It is possible to continuously monitor a wide variety of parameters through the PMBus interface. These include, but are not limited to, the parameters listed in the table below.

| Parameter           | PMBus command      |  |  |  |

|---------------------|--------------------|--|--|--|

| Input voltage       | READ_VIN           |  |  |  |

| Output voltage      | READ_VOUT          |  |  |  |

| Output current      | READ_IOUT          |  |  |  |

| Temperature*        | READ_TEMPERATURE_1 |  |  |  |

| Switching frequency | READ_FREQUENCY     |  |  |  |

| Duty cycle          | READ_DUTY_CYCLE    |  |  |  |

<sup>\*</sup> reports the temperture from temperature sensor set in command 0xDC, internal (controller IC)/external (temp. sensor)

### Monitoring faults

Fault conditions can be detected using the SALERT pin, which will be asserted low when any number of pre-configured fault or warning conditions occurs. The SALERT pin will be held low until faults and/or warnings are cleared by the CLEAR\_FAULTS command, or until the output voltage has been re-enabled. It is possible to mask which fault conditions should not assert the SALERT pin by the command SMBALERT\_MASK. In response to the SALERT signal, the user may read a number of status commands to find out what fault or warning condition occurred, see table below.

| Fault and warning    | PMBus command              |  |  |

|----------------------|----------------------------|--|--|

| Overview, Power Good | STATUS_BYTE<br>STATUS_WORD |  |  |

| Output voltage level | STATUS _VOUT               |  |  |

| Output current level | STATUS_IOUT                |  |  |

| Input voltage level  | STATUS_INPUT               |  |  |

| Temperature level    | STATUS_TEMPERATURE         |  |  |

| PMBus communication  | STATUS_CML                 |  |  |

| Miscellaneous        | STATUS_MFR_SPECIFIC        |  |  |

# General PMBus comand summary

PMBus signal interfaces characteristics

| Characteristic                                | conditions                                     | minimum | typical                                | maximum | unit |

|-----------------------------------------------|------------------------------------------------|---------|----------------------------------------|---------|------|

| PMBus signal interface cl                     | naracteristics                                 |         |                                        |         |      |

| Input clock frequency drift                   | External sync.                                 | -4      |                                        | 4       | %    |

| Initialization time                           | From VI > 27 V to ready to                     |         | 15                                     |         | ms   |

| Output voltage total on                       | Enable by input voltage                        |         | T <sub>INIT</sub> + T <sub>ONdel</sub> |         |      |

| delay time                                    | Enable by RC or CTRL pin                       |         | Tondel                                 |         |      |

| Logic output low signal                       | SCL, DA, SYNC, GCB,<br>SALERT, PG, sink/source |         |                                        | 0.4     | V    |

| Logic output high signal                      | current = 4 mA                                 | 2.6     |                                        |         | V    |

| Logic output low sink                         |                                                |         |                                        | 5       | mA   |

| Logic output high source                      |                                                |         |                                        | 5       | mA   |

| Logic input low threshold                     | SCL, SDA, CTRL, SYNC                           |         |                                        | 0.6     | V    |

| Logic input high threshold                    |                                                | 2.1     |                                        |         | V    |

| Logic pin input                               | SCL, SDA, CTRL, SYNC                           |         | 1.5                                    |         | pF   |

| Supported SMBus                               |                                                | 100     |                                        | 400     | kHz  |

| SMBus bus free time                           | STOP bit to START bit                          |         | 1.3                                    |         | μs   |

| SMBus SDA setup time from SCL                 |                                                |         | 100                                    |         | μs   |

| SMDBus SDA hold time                          |                                                |         | 0                                      |         | ns   |

| SMBus START/STOP<br>condition setup/hold time |                                                |         | 600                                    |         | ns   |

| SCL low period                                |                                                | 1.3     |                                        |         | μs   |

| SCL high period                               |                                                |         | 0.6                                    | 50      | μs   |