PoL converters provide staying power for FPGAs

Introduction

Any circuit designer will tell you that factors such as performance and flexibility are critical in many successful aspects of modern electronic design. Here at Flex Power Modules we know that although software-driven devices such as microcontrollers are adequate in many instances, there are just as many applications that require the performance of a hardware-based approach. For this reason, Field Programmable Gate Arrays (FPGAs) have become highly popular, but there is a problem – their power needs can be somewhat complex. Thankfully, a solution can be reached by adopting the latest point-of-load (PoL) converters, as an increasing number of design engineers among you are discovering.

The benefits of FPGAs over custom-designed ASICs have been well documented, and include lower cost, a wide range of sizes and the potential to reconfigure circuits. On the flip side, FPGAs demand state-of-the-art power solutions. But just how state-of-the-art? Well, we’re aware of some instances in which the power module has to offer up to 10 separate rails, as well as ‘on-the-fly’ voltage reconfiguration.

A large number of FPGAs feature transceivers that require I/O voltages to be reconfigured ‘on-the-fly’, which in turn means that the power system must be software configurable. Although the currents here are relatively low, there is a growing demand that FPGAs have configurable core voltages at high currents, promoting the use of dynamically managed energy consumption. This development will require the main supply rail to also be configurable, giving designers another challenge, often known as Adaptive Voltage Scaling (AVS).

PoL converters for FPGAs makes sense

FPGA power consumption is typically the sum of several parts that comprise a static and dynamic element, along with specific power requirements for sections like the transceiver or I/O. We can break this down further by stating that the static part mainly derives from a combination of bias and leakage currents, while the dynamic element depends largely on the particular circuit design or application, the configuration of the I/O section and the chosen clock frequency.

We know from experience that low voltages are a particular challenge. The sub-Volt range required for the core logic of FPGAs leads to high currents. In turn, large losses are created and, as you might guess, excessive heat is generated in the system.

So what else are we up against? In short, quite a lot. Sequencing multiple voltage rails, for example, can prove fairly arduous, as can meeting minimum and maximum ramp-up times when powering-up. Then there is the general intolerance of FPGAs to inaccurate voltages, which demands tight voltage tolerances on the supply, driving up your project’s complexity and cost.

Non-isolated, DC/DC point-of-load converters to the rescue

Despite all of these headaches and obstacles, you’ll be pleased to learn that the latest digitally controlled, non-isolated, DC/DC point-of-load converters offer many of the features needed for a successful implementation. In a common scenario involving FPGAs, the first rail to rise is normally the internal core voltage, followed by the I/O voltage rail and the auxiliary rail. By deploying separate PoL modules for each rail, sequencing time delays can be configured in line with the specification of the FPGA.

To demonstrate the prowess of this technology, our team at Flex Power Modules recently determined that the majority of the power needs of AMD-Xilinx's Virtex Ultrascale+ VCXU13P FPGA could be met using just three types of our PoL modules.

Firstly, the 0.85 V main core voltage at approximately 100 A was supplied using a Flex high-performance BMR467 DC/DC PoL converter, which provides up to 120 A of output current at voltages between 0.6 V and 1.8 V, thus comfortably meeting the FPGA’s requirements, even for the Vlow version with Vccint running at 0.72 V. With a footprint of just 50.8 mm x 19.05 mm x 10.4 mm, easy placement close to the FPGA was possible, minimizing the length of high current traces.

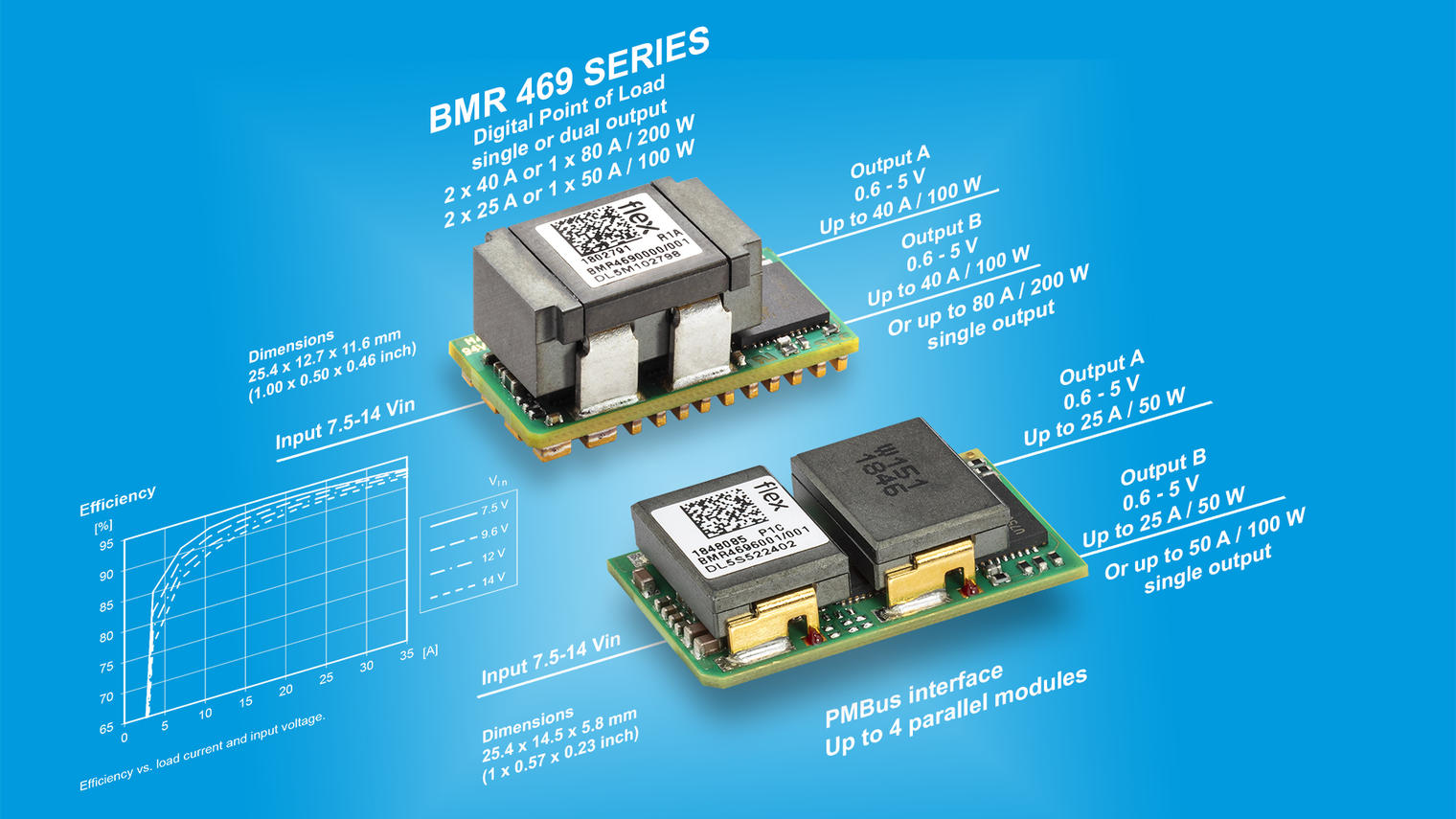

Also included in the solution were our BMR461 and BMR4696001 PoL converters. Notably, the latter can be configured for either single- or dual-output applications, meaning that a single device can take care of two different FPGA voltage rails to save cost and board area.

Our digital range of PoLs incorporate output voltage programming that supports core and I/O voltages from 0.6V to 5.5 V. Furthermore, in-built AVS over PMBus allows designers to reduce energy consumption significantly.

We should also point out that our intelligent PoLs are based on a control loop with fast transient response, making them perfect for handling the load fluctuations typical of FPGA applications. The control loop parameters can be configured digitally and dynamic compensation is offered on certain devices.

Power design software enables optimization

Those looking to maximize the potential of our high power density, high-efficiency PoL modules (and the FPGA design) will definitely gain from adopting Flex Power Designer software, a free-of-charge design tool for electronics engineers. All PoL parameters can be configured using the software, which can also monitor power modules and generate graphs of important parameters, like temperature against time. In fact, we introduced thermal simulation, a unique feature for this type of software, as part of a recent upgrade.

Ultimately, the advent of the latest PoL converters and associated software means that designing power solutions for the latest FPGAs – with their complex multi-rail requirements, timing needs and high-power levels – is far less daunting than ever before.

The next generation of the Flex Power Designer is set to include a reference design tool for AMD-Xilinx FPGAs, which will automatically suggest suitable parts for each rail. These will be optimized for cost or for performance when importing AMD-Xilinx power estimator files. There will also be a AMD-Xilinx load-based design feature to enable easier and accurate load simulation based on the needs of the AMD-Xilinx FPGAs.

Update: You can watch a recent webinar about this functionality HERE

To keep up to date with our latest Product News and Announcements, please sign-up to our Newsletter